# Memories for Graphics Systems

16M Synchronous Graphics RAM SGRAM

HYB39S16320TQ-6

HYB39S16320TQ-7

HYB39S16320TQ-8

**Version 2.1.00**

Preliminary Information SGRAM 1.1999

| HYB39S163<br>Revision His                     |              | Current Version 2.1.00                                                 |  |  |

|-----------------------------------------------|--------------|------------------------------------------------------------------------|--|--|

| Previous Ver                                  | sion: 1.x.xx |                                                                        |  |  |

| Page Page (in previous Version) Page Version) |              | All versions with major number 1 (1.x.xx) are replaced by this version |  |  |

| Previous Ver                                  | sion: 2.0.00 |                                                                        |  |  |

| 30 30 I                                       |              | CC3P in table "Operating Currents" changed                             |  |  |

| 32 32 t,                                      |              | t <sub>AH</sub> in table "AC Characteristics" changed                  |  |  |

#### **Edition 1.1999**

This edition was realized using the software system FrameMaker®.

Published by Siemens AG, Bereich Halbleiter, Marketing-Kommunikation, Balanstraße 73, 81541 München

© Siemens AG 1999.

All Rights Reserved.

#### Attention please!

As far as patents or other rights of third parties are concerned, liability is only assumed for components, not for applications, processes and circuits implemented within components or assemblies.

The information describes the type of component and shall not be considered as assured characteristics.

Terms of delivery and rights to change design reserved.

For questions on technology, delivery and prices please contact the Semiconductor Group Offices in Germany or the Siemens Companies and Representatives worldwide (see address list).

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Siemens Office, Semiconductor Group.

Siemens AG is an approved CECC manufacturer.

#### **Packing**

Please use the recycling operators known to you. We can also help you – get in touch with your nearest sales office. By agreement we will take packing material back, if it is sorted. You must bear the costs of transport.

For packing material that is returned to us unsorted or which we are not obliged to accept, we shall have to invoice you for any costs incurred.

Components used in life-support devices or systems must be expressly authorized for such purpose! Critical components<sup>1</sup> of the Semiconductor Group of Siemens AG, may only be used in life-support devices or systems<sup>2</sup> with the express written approval of the Semiconductor Group of Siemens AG.

- 1 A critical component is a component used in a life-support device or system whose failure can reasonably be expected to cause the failure of that life-support device or system, or to affect its safety or effectiveness of that device or system.

- 2 Life support devices or systems are intended (a) to be implanted in the human body, or (b) to support and/or maintain and sustain human life. If they fail, it is reasonable to assume that the health of the user may be endangered.

# Synchronous Graphics RAM

**SGRAM**

HYB39S16320TQ-6

HYB39S16320TQ-7

HYB39S16320TQ-8

User's Manual 1.1999

#### 1 Overview

• High Performance:

|                  | -6  | -7  | -7  | -8  | Unit |

|------------------|-----|-----|-----|-----|------|

| f <sub>CK</sub>  | 166 | 125 | 125 | 125 | MHz  |

| latency          | 3   | 2   | 3   | 3   | #    |

| t <sub>CK3</sub> | 6   | 8   | 7   | 8   | ns   |

| t <sub>AC3</sub> | 5.5 | 5.5 | 5.5 | 6   | ns   |

- Single Pulsed RAS Interface

- Programmable CAS Latency: 2, 3

- Fully Synchronous to Positive Clock Edge

- Programmable Wrap Sequence : Sequential or Interleave

- Programmable Burst Length:

- 1, 2, 4, 8 and full page for sequential

- 1, 2, 4, 8 for interleave

- · Special Mode Registers

- · Two color registers

- Burst Read with Single Write Operation

- Block Write and Write-per-Bit Capability

- Byte controlled by DQM0-3

- Auto Precharge and Auto Refresh Modes

- Suspend Mode and Power Down Mode

- 2k refresh cycles / 32 ms

- $t_{AC} = 5.5$ ns

- $t_{SETUP} / t_{HOLD} = 2ns / 1ns$

- Latency 2 @ 125 MHz

- Random Column Address every CLK (1-N Rule)

- Single 3.3V +/- 0.3V Power Supply

- LVTTL compatible inputs and outputs

The HYB39S16320TQ are dual bank Synchronous Graphics DRAM's (SGRAM) organized as 2 banks x 256kBit x 32 with built-in graphics features. These synchronous devices achieve high speed data transfer rates up to 166 MHz by employing a chip architecture that prefetches multiple bits and then synchronizes the output data to a system clock. The chip is fabricated with an advanced 64MBit DRAM process technology.

The device is designed to comply with all JEDEC standards set for synchronous graphics DRAM products, both electrically and mechanically.

RAS, CAS, WE, DSF and CS are pulsed signals which are examined at the positive edge of each externally applied clock. Internal chip operating modes are defined by combinations of these signals. A ten bit address bus accepts address data in the conventional RAS / CAS multiplexing style. Ten row address bits (A0-A9) and a bank select BA are strobed with RAS. Column address bits plus a bank select are strobed with CAS.

Prior to any access operation, the CAS latency, burst length and burst sequence must be programmed into the device by address inputs during a mode register set cycle. An Auto Precharge function may be enabled to provide a self-timed row precharge. This is initiated at the end of the burst sequence. In addition, it features the write per bit, the block write and the masked block write functions. By having a programmable Mode register and Special Mode register, the system can select the best suitable modes to maximize its performance.

Operating the two memory banks in an interleave fashion allows random access operation to occur at higher rate than is possible with standard DRAMs. A sequential and gapless data rate of up to 166 MHz is possible depending on burst length, CAS latency and speed grade of the device.

Auto Refresh (CBR) and Self Refresh operation are supported.

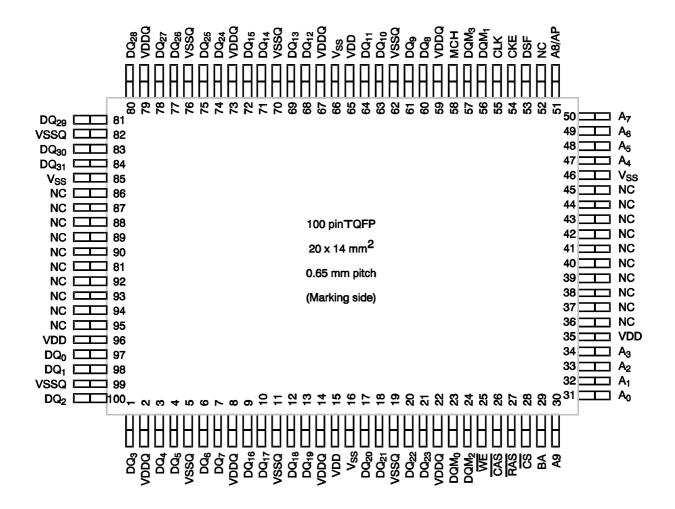

These devices operate with a single 3.3V +/- 0.3V power supply and are available in 100pin TQFP package.

#### 1.1 Features

- All signals fully synchronous to the positiv edge of the system clock

- Programmable burst lengths: 1, 2, 4, 8 or full page

- Burst data transfer in sequential or interleaved order

- · Burst read with single write

- Programmable CAS latency: 2, 3

- 8 column block write and write-per-bit modes

- Independent byte operation via DQM 0..3 interface

- Auto precharge and auto refresh modes

- 2k refresh cycles / 32 ms

- LVTTL compatible I/O

- Hidden autoprecharge for read bursts

## 1.2 Pin Configuration

Figure 1 (top view)

## 1.3 Pin Definitions and Functions

| Clock Input                |

|----------------------------|

| Clock Enable               |

| Chip Select                |

| Row Address Strobe         |

| Column Address Strobe      |

| Write Enable               |

| Address Inputs             |

| Auto Precharge             |

| Bank Select                |

| Data Input /Output         |

| Data Mask                  |

| Power (+3.3V)              |

| Ground                     |

| Power for DQ's (+ 3.3V)    |

| Ground for DQ's            |

| not connected              |

| Special Function<br>Enable |

| Must Connect High          |

|                            |

Table 1

## 1.4 Signal Pin Description

| Pin               | Туре             | Signal | Polarity        | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------------------|------------------|--------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLK               | Input            | Pulse  | Positiv<br>Edge | The system clock input. All of the SGRAM inputs are sampled on the rising edge of the clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| CKE               | Input            | Level  | Active<br>High  | Activates the CLK signal when high and deactivates the CLK signal when low. By deactivating the clock, CKE low initiates the Power Down mode, Suspend mode, or the Self Refresh mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| <del>CS</del>     | Input            | Pulse  | Active<br>Low   | CS enables the command decoder when low and disables the command decoder when high. When the command decoder is disabled, new commands are ignored but previous operations continue.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| RAS,<br>CAS<br>WE | Input            | Pulse  | Active<br>Low   | When sampled at the positive rising edge of the clock, CAS, RAS, and WE define the operation to be executed by the SGRAM.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| A0 -<br>A9        | Input            | Level  |                 | During a Bank Activate command cycle, A0-A9 defines the row address (RA0-RA9) when sampled at the rising clock edge.  During a Read or Write command cycle, A0-A7 defines the column address (CA0-CA7) when sampled at the rising clock edge.  In addition to the column address, CA8 is used to invoke autoprecharge operation at the end of the burst read or write cycle. If A8 is high, autoprecharge is selected and BA defines the bank to be precharged (low=bank A, high=bank B). If A8 is low, autoprecharge is disabled.  During a Precharge command cycle, A8 is used in conjunction with BA to control which bank(s) to precharge. If A8 is high, both bank A and bank B will be precharged regardless of the state of BA. If A8 is low, then BA is used to define which bank to precharge. |

| ВА                | Input            | Level  | _               | Selects which bank is activated. BA low selects bank A and BA high selects bank B.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| DQ0-<br>DQ31      | Input/<br>Output | Level  | _               | Data Input/Output pins operate in the same manner as on conventional DRAMs, with the exception of the Block Write function. In this case, the DQx pins perform a masking operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

Table continued on next page

Overview

| Pin               | Туре   | Signal | Polarity | Function                                                                                                                                                                                                                                                    |

|-------------------|--------|--------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DQM0<br>-<br>DQM3 | Input  | Pulse  | _        | During Read, DQM = 1 turns off the output buffers.  During Write, DQM = 1 prevents a write to the current memory location.  DQM0 corresponds to DQ0 - DQ7  DQM1 corresponds to DQ8 - DQ15  DQM2 corresponds to DQ16 - DQ23  DQM3 corresponds to DQ24 - DQ31 |

| VDD,<br>VSS       | Supply |        |          | Power and ground for the input buffers and the core logic.                                                                                                                                                                                                  |

| VDDQ<br>VSSQ      | Supply | _      | _        | Isolated power supply and ground for the output buffers to provide improved noise immunity.                                                                                                                                                                 |

| DSF               | Input  | Level  | _        | DSF is part of the input command to the SGRAM. If DSF is low, SGRAM operates in the same way as SDRAMs. When DSF is high it enables the block write and masked write and special mode register setup cycle.                                                 |

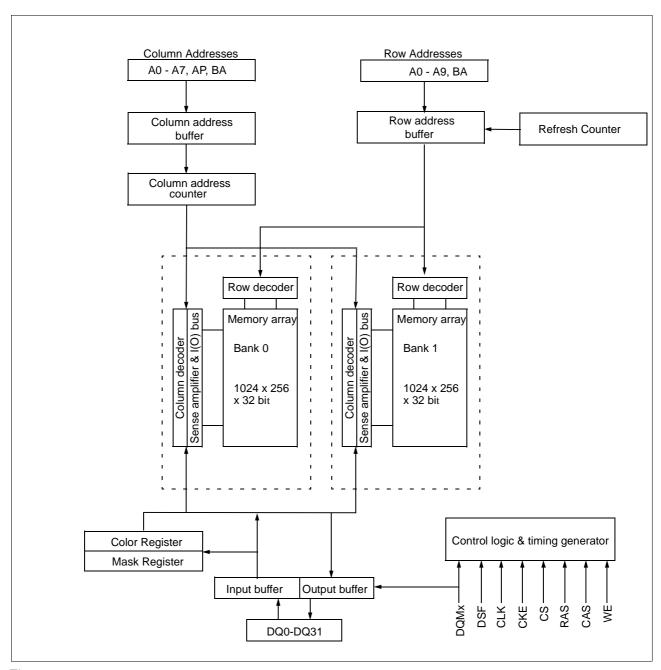

## 1.5 Functional Block Diagrams

Figure 2 Block diagram

This page is left intentionally blank

### **2** Functional Description

#### 2.1 General

The 16Mb SGRAM is a dual bank 1024 x 256 x 32 DRAM with graphics features of Block Write and Masked Write. It consists of two banks. Each bank is organized as 1024 rows x 256 columns x 32 bits.

Read and Write accesses are burst oriented. Accesses begin with the registration of an Activate command which is then followed by a Read or Write command. The address bits registered coincident with the Active command are used to select the bank and the row to be accessed. BA selects the bank and address bits A9 -A0 select the row. Address bits A7-A0 registered coincident with the Read or Write command are used to select the starting column location for the burst access.

Block Writes are not burst oriented and always apply to eight column locations selected by A7-A3. DQs registered at Block Write command are used to mask the selected columns. DQs registered coincident with the Load Special Mode Register command are used as Color Data (LC bit =1) or Persistent Mask (LM = 1). If LC and LM are both 1 in the same Load Special Mode Register command cycle, the data of the Mask and the Color Register will be unknown.

#### 2.2 Initialization

The default power on state of the mode register is supplier specific and may be undefined. The following power on and initialization sequence guarantees, that the device is preconditioned to each users specific needs.

The following sequence is recommended:

- During power on, all VDD and VDDQ pins must be built up simultaneously to the specified voltage when the input signals are held in the "NOP" state.

- The power on voltage must not exceed VDD+0.3V on any of the input pins or VDD supplies.

- The CLK signal must be started at the same time.

- After power on, an initial pause of 200 μs is required.

- The pause is followed by a precharge of both banks using the precharge command.

- To prevent data contention on the DQ bus during power on, it is required that the DQM and CKE pins be held high during the initial pause period.

- Once all banks have been precharged, the Mode Register Set Command must be issued to initialize the Mode Register.

- A minimum of eight Auto Refresh cycles (CBR) are also required.

It is also possible to reverse the last two steps of the initialization procedure:

First send at least 8 CBR commands, then the LMR command.

Failure to follow these steps may lead to unpredictable start-up modes.

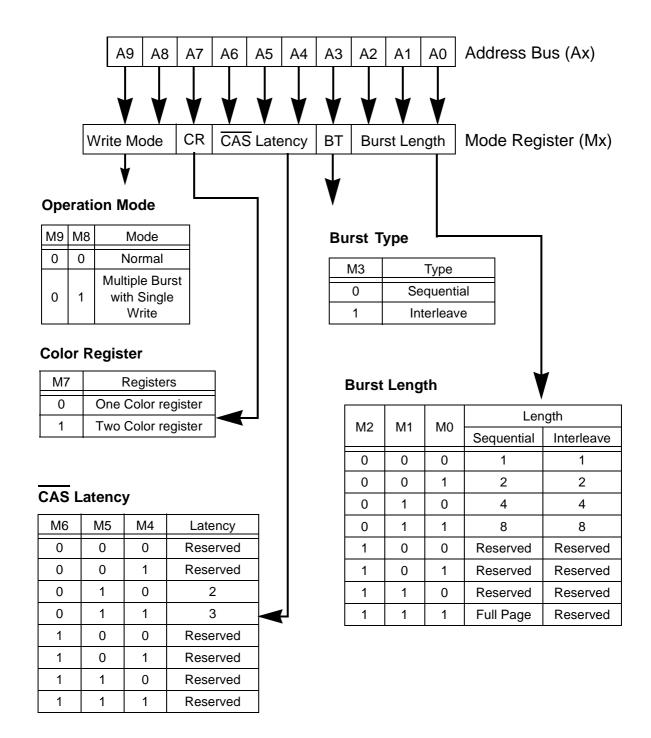

#### 2.3 Mode Register Programming

The Mode Register is used to define: a Burst Length, a Burst type, a Read Latency and an operating mode. The mode register is programmed via the Load Mode Register command and will retain the stored information until it is programmed again or the device looses power. The mode register must be loaded when both banks are idle and the controller must wait the specified time before initiating the subsequent command. Violating either of these requirements may result in unknown operation.

#### 2.3.1 Burst Length

Read and Write operations to the SGRAM are burst oriented, with the burst length being programmable. The burst length determines the maximum number of column locations that can be accessed for a given Read or Write command. Burst lengths of 1, 2, 4, or 8 locations are available for both the sequential and the interleaved burst types and a Full Page Burst is available for the sequential type. The Full Page Burst is used in conjunction with the Burst Terminate command to generate arbitrary burst lengths.

When a Read or Write command is issued, a block of columns equal to the burst length is selected. The block is defined by address bits A7-A1 when the burst length is set to 2, by A7-A2 for burst length set to 4 and by A7-A3 for burst length set to 8. The lower order bit(s) are used to select the starting location within the block. The burst will wrap within the block if a boundary is reached.

#### 2.3.2 Burst Type

Accesses within a given burst may be programmed to be either sequential or interleaved and the type is selected based on the setting of BT bit in the mode register. If BT is set to "0", the burst type is sequential, if BT is "1", the burst type is interleave.

#### 2.3.3 Read Latency

The Read Latency is the delay in clock cycles between the registration of a Read command and the availability of the first piece of output data. The latency can be set to 2 or 3 clocks. If a Read command is registered at clock edge n and the Read Latency is 2 clocks, the data will be available by clock edge n+2. The DQs will start driving already one cycle earlier (n+1).

#### 2.3.4 Color Register

The Siemens 16M SGRAM offers two Color Registers. If Bit M7 is set to "1", two Color Register mode is specified.

#### 2.3.5 Operation Mode

In normal operation, the bits M8 and M9 of Mode Register (MR) are set "0". The programmed burst length applies to both read and write bursts. When bit M8 is set to "1", burst read and single write mode is selected.

Test modes and reserved states should not be used because unknown operation or incompatibility with future versions may result.

#### 2.4 Load Special Mode Register (LSMR)

The Special Mode Register command is used to load the mask and color registers, which are used in Block Write and Masked Write cycles. The data to be written to either the color registers or the Mask Register is applied to the DQs and the control information is applied to the address inputs. During a LSMR cycle, if the address bit A6 is "1", and all other address inputs are "0", the Color Register 0 will be loaded with the data on the DQs. If the address bits A6 and A7 are both set equal to "1" and Mode Register M7 bit was already set to "1", Color Register 1 will be loaded with the data on the DQs. This color data is used for Block Write cycles. Similarly, when input A5 is "1", and all other address inputs are "0" during a LSMR cycle, the mask register will be loaded with the data on the DQs. Never Set bit A5 to "1" when A6 and/or A7 are set equal to "1" in the same Load Special Mode Register cycle to avoid unknown operation.

#### 2.4.1 Color Registers

Two Color Registers (Color Register 0 and Color Register 1) are available in the devices. Each color register is a 32-bit register which supplies the data during Block Write cycles. The Color Register is loaded via a Load Special Mode Register command, as shown in the Function Truth table and will retain data until loaded again with a new data or until power is removed from the SGRAM.

#### 2.4.2 Mask Register

The Mask Register (or the Write-per-Bit mask register) is a 32-bit register which acts as a per-bit mask during Masked Write and Masked Block Write cycles. The Mask Register is loaded via the Load Special Mode Register command and will retain data until loaded again or until power is removed from the SGRAM.

#### 2.5 Commands

The Function Truth Table provides a quick reference of available commands.

#### **Function Truth Table**

| Operation                                | CKE<br>n-1 | CKE<br>n | CS     | RAS    | CAS    | WE     | DSF    | DQM    | ВА     | A8     | A0-<br>A7 |

|------------------------------------------|------------|----------|--------|--------|--------|--------|--------|--------|--------|--------|-----------|

| Device Deselect (INHBT)                  | Н          | Х        | Ι      | Х      | Х      | Х      | Х      | Х      | X      | X      | Х         |

| No Operation (NOP)                       | Н          | Χ        | L      | Н      | Н      | Н      | Χ      | Χ      | Χ      | Χ      | Х         |

| Load Mode Register (LMR)                 | Н          | Х        | L      | L      | L      | L      | L      | Х      | Х      | OPC    | ODE       |

| Load Special Mode<br>Register (LSMR)     | Н          | Х        | L      | L      | L      | L      | Н      | Х      | Х      | OPC    | ODE       |

| Row Activate (ACT)                       | Н          | Х        | L      | L      | Н      | Н      | L      | Х      | ВА     | Row    | Addr      |

| Row Active with WpB (ACTM)               | Н          | Х        | L      | L      | Н      | Н      | Н      | Х      | ВА     | Row    | Addr      |

| Read (RD)                                | Н          | Χ        | L      | Н      | L      | Η      | Х      | Х      | ВА     | L      | Col.      |

| Read with Auto Precharge (RDA)           | Н          | Х        | L      | Н      | L      | Н      | Х      | Х      | ВА     | Н      | Col.      |

| Write Command (WR)                       | Н          | Χ        | L      | Н      | L      | L      | L      | Х      | ВА     | L      | Col.      |

| Write Command with Auto Precharge (WRA)  | Н          | Х        | L      | Н      | L      | L      | L      | Х      | ВА     | Н      | Col.      |

| Block Write (BW)                         | Н          | Х        | L      | Н      | L      | L      | Н      | Х      | ВА     | L      | Col.      |

| Block Write with Auto<br>Precharge (BWA) | Н          | Х        | L      | Н      | L      | L      | Н      | Х      | ВА     | Н      | Col.      |

| Burst Terminate (BST)                    | Н          | Х        | L      | Н      | Н      | L      | Χ      | Х      | Χ      | Х      | Χ         |

| Precharge Single Bank (PRE)              | Н          | Х        | L      | L      | Н      | L      | Х      | Х      | ВА     | L      | Х         |

| Precharge All Banks<br>(PREAL)           | Н          | Χ        | L      | L      | Н      | L      | Χ      | Х      | Χ      | Н      | Χ         |

| Auto Refresh (REF)                       | Н          | Н        | L      | L      | L      | Н      | Χ      | Χ      | Χ      | Χ      | Χ         |

| Self Refresh Entry<br>(SREF(EN))         | Н          | L        | L      | L      | L      | Н      | Х      | Х      | Х      | Х      | Х         |

| Self Refresh Exit<br>(SREF(EX))          | L<br>L     | H<br>H   | H<br>L | X<br>H | X<br>H | X<br>H | X      | X<br>X | X<br>X | X<br>X | X         |

| Power Down Mode Entry<br>(PDN-EN)        | H<br>H     | L        | H      | X<br>H | X<br>H | X<br>H | X<br>X | X      | X<br>X | X<br>X | X<br>X    |

| Power Down Mode Exit<br>(PDN-EX)         | L          | Н        | Х      | Х      | Х      | Х      | Х      | Х      | Х      | Х      | Х         |

Table 2 Notes concerning special operation see next page

- Note 01 All inputs are latched on the rising edge of the CLK.

- Note 02 LMR, REF and SREF commands should be issued only after both banks are deactivated (PREAL command).

- Note 03. ACT and ACTM command should be issued only after the corresponding bank has been deactivated (PRE command).

- Note 04. WR, WRA, RD, RDA should be issued after the corresponding bank has been activated (ACT command).

- Note 05. Auto Precharge command is not valid for full-page burst.

- Note 06. BW and BWA commands use mask register data only after ACTM command. DQM byte masking is active regardless of WPB mask.

- Note 07. Loading Mask Register: Initiate an LSMR cycle with address pin A5 =1 to load the Mask register with the Mask data present on DQ pins. Except A5, all other address pins must be "0" during LSMR cycle while loading the Mask Register

- Note 08. Loading Color Register: Initiate an LSMR cycle with address pin A6 = 1 to load the Color register with the Color input data on DQ pins. Address pin A7 selects Color register. Except A6 and A7, all other address pins must be "0" during LSMR cycle while loading a Color register. If one Color register mode is enabled, all address pins, except A6, must be "0" during LSMR cycle.

- Note 09. If BW or BWA operation is initiated and 2-Color Register Mode is initialized by the Mode Register, address A0 selects the desired Color Register for the operation. If A0 = 0, Color Register 0 will be used, if A0 = 1, Color Register 1.

- Note 010. Any Write or Block Write cycles to the selected bank/row while active will be masked according to the contents of the mask register, in addition to the DQM signals and the column/byte mask information (the later for Block Writes only).

- Note 011. Block Writes are not burst oriented and always apply to the eight column locations selected by A7-A3.

- Note 012. Addressline A9 is always "X" with the exception of two commands:

In LMR and LSMR commands it provides Opcode (see description Mode and Special Mode Register)

In ACT and ACTM commands it provides the addressbit 9 of the Row Address.

## 2.5.1 Address Input for Mode Set (Mode Register Functions)

Figure 3

## 2.5.2 Burst Length and Sequence:

#### **Burst of two**

| Starting Address<br>(Column Address A0) | Sequential<br>Addressing Sequence<br>(decimal) | Interleave Addressing<br>Sequence (decimal) |

|-----------------------------------------|------------------------------------------------|---------------------------------------------|

| 0                                       | 0, 1                                           | 0, 1                                        |

| 1                                       | 1, 0                                           | 1,0                                         |

Table 3

#### **Burst of four**

| Starting Address<br>(Column Address A1 -<br>A0) | Sequential<br>Addressing Sequence<br>(decimal) | Interleave Addressing<br>Sequence (decimal) |

|-------------------------------------------------|------------------------------------------------|---------------------------------------------|

| 0                                               | 0, 1,2,3                                       | 0, 1, 2, 3                                  |

| 1                                               | 1, 2, 3, 0                                     | 1, 0, 3, 2                                  |

| 2                                               | 2, 3, 0 , 1                                    | 2, 3, 0 ,1                                  |

| 3                                               | 3, 0, 1 , 2                                    | 3, 2, 1, 0                                  |

Table 4

## **Burst of eight**

| Starting Address<br>(Column Address A1 -<br>A0) | Sequential<br>Addressing Sequence<br>(decimal) | Interleave Addressing<br>Sequence (decimal) |

|-------------------------------------------------|------------------------------------------------|---------------------------------------------|

| 0                                               | 0,1,2,3,4,5,6,7                                | 0,1,2,3,4,5,6,7                             |

| 1                                               | 1,2,3,4,5,6,7,0                                | 1,0,3,2,5,4,7,6                             |

| 2                                               | 2,3,4,5,6,7,0,1                                | 2,3,0,1,6,7,4,5                             |

| 3                                               | 3,4,5,6,7,0,1,2                                | 3,2,1,0,7,6,5,4                             |

| 4                                               | 4,5,6,7,0,1,2,3                                | 4,5,6,7,0,1,2,3                             |

| 5                                               | 5,6,7,0,1,2,3,4                                | 5,4,7,6,1,0,3,2                             |

| 6                                               | 6,7,0,1,2,3,4,5                                | 6,7,4,5,2,3,0,1                             |

| 7                                               | 7,0,1,2,3,4,5,6                                | 7,6,5,4,3,2,1,0                             |

Table 5

#### **Full Page Burst**

Full page Burst is an extension of the above tables of sequential addressing with the burst length being 256.

#### 2.5.3 Special Mode Register Functions:

|    |    |    | Functions |    |    |    |    |    |    |                       |

|----|----|----|-----------|----|----|----|----|----|----|-----------------------|

| A9 | A8 | A7 | A6        | A5 | A4 | А3 | A2 | A1 | A0 |                       |

| 0  | 0  | 0  | 0         | 1  | 0  | 0  | 0  | 0  | 0  | Load Mask Register    |

| 0  | 0  | 0  | 1         | 0  | 0  | 0  | 0  | 0  | 0  | Load Color Register 0 |

| 0  | 0  | 1  | 1         | 0  | 0  | 0  | 0  | 0  | 0  | Load Color Register 1 |

Table 6

Note: If only one Color Register is in use, A7 is Don't Care.

#### **Special Mode Register naming conventions**

| Address bit name | Special name | Function              |

|------------------|--------------|-----------------------|

| A5               | LM           | Load Mask Enable      |

| A6               | LC           | Load Color Enable     |

| A7               | SCR          | Select Color Register |

Table 7

#### 2.5.4 Device Deselect (INHBT)

The device deselect or inhibit function prevents commands from being executed by the SGRAM, regardless of whether the CLK signal is enabled. The device is effectively deactivated (CS is high).

#### 2.5.5 No Operation (NOP)

The NOP command is used to perform a no operation to an SGRAM which is selected (CS is low). This prevents unwanted commands being registered during idle or wait states. The execution of the command(s) already in progress will not be affected

#### 2.5.6 Load Mode Register (LMR)

The Mode Register is loaded via address input pins A9 - A0 . The LMR command can only be issued when both banks are idle, and a subsequent executable command can not be issued until 2 CLK cycle Latency is met.

#### 2.5.7 Load Special Mode Register (LSMR)

LSMR command is used to load either the Color Register(s) or the Mask Register at a time. The control information is provided on inputs A9 - A0 , while the data for the Color or Mask Register is provided on the DQs. The LSMR command can be issued when both banks are idle, or one or both are active but with no Read, Write or Block Write accesses in progress.

#### 2.5.8 Active (ACT)

The ACT command is used to open (or activate) a row in a particular bank. The value on BA selects the bank and the address provided on input pins A9 - A0 selects the row. This row remains open for accesses until a Precharge command is issued to the bank. A Precharge command must be issued before opening a different row in the same bank.

#### 2.5.9 Active with WPB (ACTM)

ACTM command is similar to the ACT command, except that the Write-per-Bit mask is activated. Any Write or Block Write cycles to the selected bank/row while active will be masked according to the contents of the Mask Register.

#### 2.5.10 Read (RD)

The Read command is used to initiate a burst read access from an active row. The value on BA selects the bank and the address provided on inputs A7 - A0 selects the starting column location. The value on A8 determines whether or not Auto Precharge is used. If A8 is "1", Auto Precharge is used. If Auto Precharge is selected, the row being accessed will be precharged at the end of the read burst; if Auto Precharge is not selected, the row will remain open for subsequent accesses. If a particular DQM was registered high, the corresponding DQs appearing 2 clocks later on the output pins will be High-Z.

#### 2.5.11 Write (WR)

The Write command is used to initiate a burst write access to an active row. The value on BA selects the bank and the address provided on inputs A7 -A0 selects the starting column location. The value on A8 determines whether or not Auto Precharge is used. If A8 is "1", Auto Precharge is used. If Auto Precharge is selected, the row being accessed will be precharged at the end of write burst; if Auto Precharge is not selected, the row will remain open for subsequent accesses. If a particular DQM is registered high, the corresponding data inputs will be ignored and the write will not be executed to that byte location.

#### 2.5.12 Block Write (BW)

The Block Write command is used to write a single data value to the block of eight consecutive column locations addressed by inputs A7 - A3 . The data is provided by the Color Register which must be loaded prior to the Block Write cycle by invoking LSMR cycle. If the two Color Register option is enabled, the address line A0 is used to select the desired Color Register. A "0" at A0 selects Color Register 0, a "1" Color Register 1. The input data on DQs which is registered coincident with the Block Write command is used to mask specific column/byte combinations within the block. The DQM signals operate the same way as for Write cycles, but are applied to all eight columns in the selected block.

#### 2.5.13 Precharge (PRE)

The Precharge command is used to deactivate the open row in a particular bank or the open row in both banks. The bank(s) will be available for row access some specified time (tRP) after the Precharge command is issued. Input A8 determines whether one or both banks are to be precharged, input BA selects the bank. If A8 is "1", both banks are to be precharged and BA is "don't care." Once a bank is precharged (or deactivated), it is in the idle state and must be activated prior to any Read, Write, or Block Write commands being issued to that bank.

#### 2.5.14 Auto Precharge (PREA)

The Auto Precharge feature allows the user to issue a Read, Write, or Block Write command that automatically performs a precharge upon the completion of the Block Write access or Read or Write burst, except in the Full Page Burst mode, where it has no effect. The use of this feature eliminates the need to "manually" issue a Precharge command during the functional operation of the SGRAM.

#### 2.5.15 Burst Terminate (BST)

The Burst Terminate command is used to truncate either fixed-length or Full Page Bursts.

#### 2.5.16 Auto Refresh (REF)

Auto Refresh is used to refresh the various rows in the SGRAM and is analogous to CAS-before-RAS (CBR) in DRAMs. This command must be issued each time a refresh is required. The addressing is generated by the internal refresh counter, therefore, the address bits are "don't care" during a CBR cycle. The SGRAM requires that 2048 rows to be refreshed every 32ms (t<sub>REF</sub>). This refresh can be accomplished either by providing a Auto Refresh command every 15.6µs or all 2048 Auto Refresh commands can be issued in a burst at the minimum cycle rate (tRC) once every 32ms.

**Functional Description**

### 2.5.17 Self Refresh (SREF)

The Self Refresh command can be used to retain data in the SGRAM, even if the rest of the system is powered down. When in the Self Refresh mode, the SGRAM retains data without external clocking. Once the SREF command is registered, all the inputs to the SGRAM become "don't care" with the exception of CKE, which must remain low. Once SREF mode is engaged, the SGRAM provides its own internal clocking, causing it to perform its own Auto Refresh cycles. The SGRAM may remain in Self Refresh mode for an indefinite period. The procedure for exiting requires a sequence of commands. First, the system clock must be stable prior to CKE going high. Once CKE is high, the SGRAM must have NOP commands issued for  $t_{SRX}$ , because of the time required for the completion of any bank currently being internally refreshed.

# 2.6 Detailed Description of WRITE COMMANDS (WR, Masked Writes, Block Write)

#### 2.6.1 Write Command (WR)

The following pages illustrate the Write operations for various cases

#### **Summary Write Commands**

| Mnemonic | CKE | CS | RAS | CAS | WE | DSF | DQM | ВА | A8 | Address<br>Lines |

|----------|-----|----|-----|-----|----|-----|-----|----|----|------------------|

| WR       | Н   | L  | Н   | L   | L  | L   | 0   | ВА | L  | Column           |

| WRA      | Н   | L  | Н   | L   | L  | L   | 0   | ВА | Н  | Column           |

| BW       | Н   | L  | Н   | L   | L  | Н   | 0   | ВА | L  | Column           |

| BWA      | Н   | L  | Н   | L   | L  | Н   | 0   | ВА | Н  | Column           |

Table 8

Note: Input data at DQ pins at Block Write command is registed as a column mask for that block

of columns

Note: Explanation of Mnemonics:

WR: Write Command

WRA: Write Command with Auto Precharge

BW: Block Write

BWA: Block Write with Auto Precharge

BA: Bank Select

Write bursts are initiated with a Write command. The starting column and bank address is provided with the Write command, normal or Block Write is selected, and Auto Precharge is either enabled or disabled for that access. If Auto Precharge is enabled, the row being accessed is precharged automatically at the completion of the burst.

During Write bursts, the first valid data-in element will be registered coincident with the Write command. Sub-sequent data elements will be registered on successive positive clock edge. Upon completion of a fixed-length burst, assuming no other commands have been initiated, the DQs will remain High-Z, and any additional data will be ignored. A full-page burst will continue until terminated (at the end of the page, it will wrap to column 0 and continue).

A fixed-length Write burst may be followed by, or truncated with a subsequent Write burst or Block Write command (provided that Auto Precharge was not activated) and a full page Write burst can be truncated with a subsequent Write burst or Block Write command. The new Write or Block Write command can be issued on any clock following the previous Write command, and the data provided coincident with the new command applies to the new command. To truncate a Block Write, the  $t_{BWC}$  parameter has to be met.

#### **Functional Description**

A fixed-length Write burst may be followed by, or truncated with a subsequent Read burst (provided that Auto Precharge was not activated) and a full-page Write burst can be truncated with a subsequent Read burst. Once the Read command is registered, the data inputs will be ignored, and writes will not be executed.

A fixed-length Write burst may be followed by, or truncated with a Precharge command to the same bank (provided that Auto Precharge was not activated) and a full-page Write burst may be truncated with a Pre-charge command to the same bank. The Precharge command should be issued x cycles ( $x = t_{WR} / t_{CK}$  rounded up to the next whole number) after the clock edge at which the last desired input data element is registered. In addition, the DQM signals must be used to mask input data, starting with the clock edge following the last desired data element and ending with the clock edge on which the Precharge command is entered. A Precharge command issued at the optimum time provides the same operation that would result from the same fixed-length Burst with Auto Precharge.

### 2.6.2 Disadvantages of Write command with Auto Precharge

- 1. Back to back Read/Write bursts can not be initiated. The Read/Write command with Auto Precharge will automatically initiate a precharge of the row in the selected bank. Most of the applications require subsequent Read/Write bursts in the same page.

- 2. The Auto Precharge command does not allow truncation of fixed-length bursts. It also does not apply to Full Page bursts.

#### 2.6.3 Terminating a Write burst

The fixed-length or Full-Page Write bursts can be truncated with the Burst Terminate command. When truncating a Write burst, the input data applied one clock edge prior to the Burst Terminate command will be the last data written.

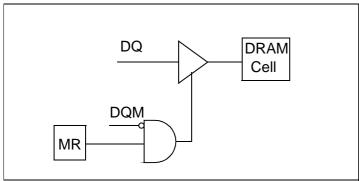

#### 2.6.4 Masked Writes

Any Write performed to a row that was activated via an Active with WPB command is a Write-per-Bit-Mask (WPBM). Data is written to the 32 cells at the selected column location subject to the mask stored in the WPB mask register. The data to be written in the DRAM cell will be according to the following mask:

#### **Write Masking Function Representation**

| DQM | MR | DRAM Cell |

|-----|----|-----------|

| 0   | 0  | Mask      |

| 1   | 0  | Mask      |

| 1   | 1  | Mask      |

| 0   | 1  | Write     |

Table 9

Symbolic representation of Write Masking Function

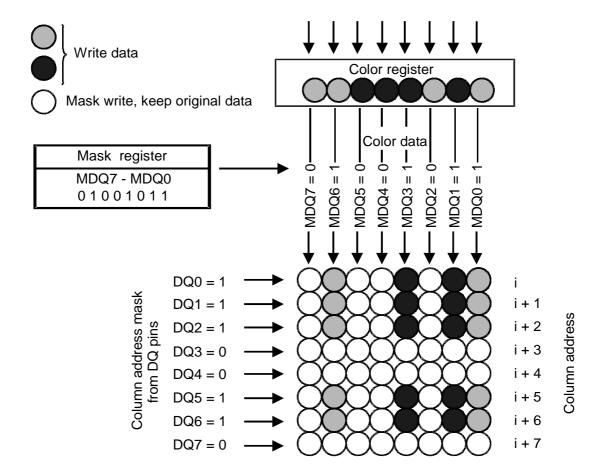

Figure 4

If a particular bit in the WPB mask register is a "0", the data appearing on the corresponding DQ input will be ignored, and the existing data in the corresponding DRAM cell will remain unchanged. If a mask data is a "1", the data appearing on the corresponding DQ input will be written to the corresponding DRAM cell. The overall Write mask consists of a combination of the DQM inputs, which will mask on a per-byte basis, and the WPB mask register, which masks on a per-bit basis.

If a particular DQM signal was registered high, the corresponding byte will be masked. A given bit is written if the corresponding DQM signal registered is "0" and the corresponding WPB mask register bit is "1".

Note that the DQM Latency for Write is zero.

#### 2.6.5 Block Write (BW)

Each Block Write cycle writes a single data value from a Color Register to the block of eight consecutive column locations addressed by A7 - A3. If Single Color Register Mode is enabled, the content of Color Register 0 is written. If both Color Registers are enabled, address pin A0 selects the desired Color Register. Address A0 = 0 selects Color Register 0, address pin A0 = 1 Color Register 1. The information on the DQs which is registered coincident with the Block Write command is used to mask specific column/byte combinations within the block.

| Address                    | Byte within data word |      |        |        |  |  |  |  |  |

|----------------------------|-----------------------|------|--------|--------|--|--|--|--|--|

| within<br>written<br>block | Byte 3 Byte           |      | Byte 1 | Byte 0 |  |  |  |  |  |

| 0                          | DQ24                  | DQ16 | DQ8    | DQ0    |  |  |  |  |  |

| 1                          | DQ25                  | DQ17 | DQ9    | DQ1    |  |  |  |  |  |

| 2                          | DQ26                  | DQ18 | DQ10   | DQ2    |  |  |  |  |  |

| 3                          | DQ27                  | DQ19 | DQ011  | DQ3    |  |  |  |  |  |

| 4                          | DQ28                  | DQ20 | DQ12   | DQ4    |  |  |  |  |  |

| 5                          | DQ29                  | DQ21 | DQ13   | DQ5    |  |  |  |  |  |

| 6                          | DQ30                  | DQ22 | DQ14   | DQ6    |  |  |  |  |  |

| 7                          | DQ31                  | DQ23 | DQ15   | DQ7    |  |  |  |  |  |

Bit Mask mapping of DQ bits

Table 10

The table shows the masking of data caused by the registered value on the DQ pins, when data is transfered from Color Register to the 8 succeeding memory locations addressed in the Write Block command.

When a "1" is registered, the Color Register data will be written to the corresponding DRAM cells, subject to the DQM and the WPB masking. The overall Block Write mask consists of a combination of the DQM signals, the WPB mask register and the column/byte mask information.

#### 2.6.6 Block Write Timing Considerations.

A Block Write access requires a time period of  $t_{BWC}$  to execute, so in general, the cycle after the Block Write command should be a NOP. However, Active or Precharge commands to the other bank are allowed. When following a Block Write with a Precharge command to the same bank,  $t_{BPL}$  must be met.

#### **Block Write Illustration:**

Write-per-Bit

Mask data = Mask register + DQMi

Note: Only single Color Register and Byte 0 of Color Register is used in this example.

#### **Electrical Characteristic**

#### 3 Electrical Characteristic

## 3.1 Absolute Maximum Ratings

| Operating temperature range                             | 0 to + 70 °C                     |

|---------------------------------------------------------|----------------------------------|

| Storage temperature range                               | – 55 to + 150 °C                 |

| Input/output voltage                                    | – 0.3 to V <sub>DD</sub> + 0.3 V |

| Power supply voltage V <sub>DD</sub> / V <sub>DDQ</sub> | – 0.3 to + 4.6 V                 |

| Power Dissipation                                       | 1 W                              |

| Data out current (short circuit)                        | 50 mA                            |

Note: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage of the device. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **Electrical Characteristic**

#### **Recommended Operation and DC Characteristics**

| Parameter                                                                                                                | Symbol                               | Limit \    | Unit                 | Notes |      |

|--------------------------------------------------------------------------------------------------------------------------|--------------------------------------|------------|----------------------|-------|------|

| Falametei                                                                                                                | Symbol                               | min.       | max.                 | Offic |      |

| Input high voltage                                                                                                       | $V_{ m IH}$                          | 2.0        | V <sub>DD</sub> +0.3 | V     | 2, 3 |

| Input low voltage                                                                                                        | $V_{\scriptscriptstyle \mathrm{IL}}$ | - 0.3      | 0.8                  | V     | 2, 3 |

| Output high voltage ( $I_{OUT} = -2.0 \text{ mA}$ )                                                                      | $V_{OH}$                             | 2.4        | _                    | V     |      |

| Output low voltage ( $I_{OUT} = 2.0 \text{ mA}$ )                                                                        | $V_{OL}$                             | _          | 0.4                  | V     |      |

| Input leakage current, any input $(0 \text{ V} < V_{\text{IN}} < 3.6 \text{ V}, \text{ all other inputs} = 0 \text{ V})$ | $I_{\scriptscriptstyle  m I(L)}$     | <b>- 5</b> | 5                    | μΑ    |      |

| Output leakage current (DQ is disabled, 0 V < $V_{\rm OUT}$ < $V_{\rm DD}$ )                                             | $I_{O(L)}$                           | <b>–</b> 5 | 5                    | μΑ    |      |

#### Table 11

*Note:* 1)  $T_A = 0$  to  $70 \,^{\circ}C$ ;  $V_{SS} = 0$  V;  $V_{DD}, V_{DDQ} = 3.3 \text{ V} \pm 0.3 \text{ V}$

2) All voltages are referenced to  $V_{ss}$

3)  $V_{IH}$  may overshoot to  $V_{DD}$  + 2.0V for pulse width of <4ns with 3.3V.

$V_{IL}$  may undershoot to -2.0V for pulse width <4ns with 3.3V.

Pulse width measured at 50% points with amplitude measured peak to DC reference.

#### Capacitance

| Parameter                                               | Symbol          | max. Values | Unit |

|---------------------------------------------------------|-----------------|-------------|------|

| Input capacitance (A0 to A9,BA)                         | $C_{\text{I1}}$ | 4           | pF   |

| Input capacitance (RAS, CAS, WE, CS, CLK, CKE, DQM,DSF) | $C_{12}$        | 4           | pF   |

| Output capacitance (DQ)                                 | $C_{\text{IO}}$ | 6           | pF   |

Table 12

Note:  $T_{\rm A}$  = 0 to 70 °C;  $V_{\rm DD}$  = 3.3 V  $\pm$  0.3 V, f = 1 MHz

## **Electrical Characteristic**

## 3.2 Operating Currents

## **Operating Currents Table**

| Parameter                              | Sym-                | Test Condition                                       | CAS     | -6  | -7   | - 8 | Unit  | Note |

|----------------------------------------|---------------------|------------------------------------------------------|---------|-----|------|-----|-------|------|

| Tarameter                              | bol                 | rest condition                                       | Latency |     | max. |     |       |      |

| Operating                              | loo1                | trc>=trc (min.)                                      | 3       | 200 | 200  | 180 | A     | 4    |

| Current                                | Icc1                | tck>=tck(min.), IO = 0mA                             | 2       | 180 | 180  | 170 | mA    | 4    |

| Precharge<br>Standby                   | I <sub>cc2</sub> P  | CKE<=VIL(max), tck=tck(m                             | in.)    | 3   | 3    | 3   | mA    | 4    |

| Current in<br>Power Down<br>Mode       | I <sub>cc2</sub> PS | CKE<=VIL(max), tck=infinite                          | е       | 2   | 2    | 2   | mA    |      |

| Precharge<br>Standby                   | I <sub>cc2</sub> N  | CKE>=VIH(min), tck>=tck(ninput changed once in 30 ns | •       | 60  | 60   | 60  | mA    | 4    |

| Current in Non-<br>power down<br>Mode  | I <sub>cc2</sub> NS | S CKE>=VIH(min), tck=infinite, no input change       |         | 15  | 15   | 15  | mA    |      |

| Active Standby<br>Current in           | I <sub>cc3</sub> P  | CKE<=VIL(max), tck>=tck(r                            | nin.)   | 6   | 6    | 6   | mA    |      |

| Power Down<br>Mode I <sub>cc3</sub> PS |                     | CKE<=VIL(max), tCK=infini                            | 6       | 6   | 6    |     |       |      |

| Active Standby<br>Current in           | I <sub>cc3</sub> N  | CKE>=VIH(min), tck>=tck(ninput changed every 30 ns   | nin.)   | 90  | 90   | 90  | m ^   |      |

| Non-power<br>Down Mode                 | I <sub>cc3</sub> NS | CKE>=VIH(min),tck=infinite no input change           | 30      | 30  | 25   | mA  |       |      |

| Burst Operating                        | 1 4                 | Burst Length = full page trc = infinite,             | 3       | 200 | 200  | 190 | mA    | 4, 5 |

| Current                                | I <sub>CC</sub> 4   | tck >= tck(min.), Io = 0 mA<br>2 banks interleave    | 2       | 200 | 200  | 190 | 111/4 | 7, 0 |

| Auto (CBR)                             |                     |                                                      | 3       | 170 | 170  | 160 |       |      |

| Refresh<br>Current                     | I <sub>cc5</sub>    | trc>=trc(min)                                        | 2       | 160 | 160  | 160 | mA    | 4    |

| Self Refresh<br>Current                | I <sub>cc6</sub>    | CKE=<0,2V                                            |         | 2   | 2    | 2   | mA    |      |

| Operating<br>Current (Block<br>Write)  | Icc7                | tck >= tck (min.), lo = 0 mA<br>tBWC = tBWC(min.)    |         | 200 | 200  | 190 | mA    |      |

Table 13 Notes see next page

#### **Electrical Characteristic**

Note: 1) TA = 0 to  $70 \,^{\circ}C$ ,  $V_{DD} = 3.3V \pm 0.3V$

- 2) These are recommended operating conditions unless otherwise noted

- 3) All values are preliminary and subject to future change

- 4) These parameters depend on the cycle rate and these values are measured by the cycle rate under the minimum value of  $t_{CK}$  and  $t_{RC}$ .

Input signals are changed one time during  $t_{CK}$ .

5) These parameters depend on output loading. Specified values are obtained with output open.

## **Electrical Characteristic**

## 3.3 AC Characteristics

|                                               | •     | Limit Values     |     |      |     |      |     |      |      |      |

|-----------------------------------------------|-------|------------------|-----|------|-----|------|-----|------|------|------|

| Parameter                                     | La-   | Sym-<br>bol      | bol |      | -   | · 7  | -   | · 8  | Unit | Note |

|                                               | tency | 201              | min | max  | min | max  | min | max  |      |      |

| Clock and Clock Enable                        |       |                  |     |      |     |      |     |      |      |      |

| Clock Cycle Time                              | 3     | t <sub>CK3</sub> | 6   |      | 7   |      | 8   |      | ns   |      |

|                                               | 2     | $t_{CK2}$        | 8   |      | 8   |      | 10  |      | ns   |      |

| System frequency                              | 3     |                  |     | 166  |     | 143  |     | 125  | MHz  |      |

|                                               | 2     |                  |     | 125  |     | 125  |     | 100  | MHz  |      |

| Clock Access Time                             | 3     | $t_{AC3}$        |     | 5.5  |     | 5.5  |     | 6    | ns   | 3    |

| (for 30 pF load)                              | 2     | $t_{AC2}$        |     | 5.5  |     | 5.5  |     | 6    | ns   | 3    |

| Clock High Pulse Width                        |       | $t_{CH}$         | 2.5 | ı    | 3   | 1    | 3   | ı    | ns   |      |

| Clock Low Pulse Width                         |       | $t_{CL}$         | 2.5 | 1    | 2.5 | 1    | 3   | 1    | ns   |      |

| CKE Setup Time                                |       | $t_{CKS}$        | 2   | -    | 2   | _    | 2.5 | -    | ns   |      |

| CKE Hold Time                                 |       | $t_{CKH}$        | 1   | ı    | 1   | _    | 1   | ı    | ns   |      |

| Transition time (rise and fall)               |       | $t_{T}$          | 0.5 | 10   | 0.5 | 10   | 0.5 | 10   | ns   |      |

| Common Parameters                             |       |                  |     |      |     |      |     |      |      |      |

| Command Setup time                            |       | $t_{CS}$         | 2   | -    | 2   | _    | 2.5 | -    | ns   | 4    |

| Command Hold Time                             |       | $t_{CH}$         | 1   | ı    | 1   | 1    | 1   | ı    | ns   |      |

| Address Setup Time                            |       | $t_{AS}$         | 2   | ı    | 2   | _    | 2.5 | ı    | ns   | 4    |

| Address Hold Time                             |       | $t_{AH}$         | 1.3 | ı    | 1.3 | -    | 1.3 | ı    | ns   |      |

| Active to Read or Write delay                 |       | $t_{RCD}$        | 18  | ı    | 21  | 1    | 24  | ı    | ns   | 5    |

| Cycle Time                                    |       | $t_{RC}$         | 66  | ı    | 70  | -    | 80  | ı    | ns   | 5    |

| Active to Precharge command period            |       | $t_{RAS}$        | 48  | 100k | 49  | 100k | 56  | 100k | ns   | 5    |

| Row Precharge Time                            |       | $t_{RP}$         | 18  | _    | 21  | _    | 24  | _    | ns   | 5    |

| Active Bank A to Active Bank I command period | В     | $t_{RRD}$        | 12  | _    | 14  | _    | 16  | _    | ns   | 5    |

| CAS to CAS delay time (same                   | bank) | $t_{\sf CCD}$    | 1   | _    | 1   | _    | 1   | ı    | CLK  |      |

Table continued on next page.

## **Electrical Characteristic**

|                                  | CAS    | 0               |     |             | Limit | Values |                      |     |      |      |

|----------------------------------|--------|-----------------|-----|-------------|-------|--------|----------------------|-----|------|------|

| Parameter                        | La-    | Sym-<br>bol     | -   | - 6         | -     | · 7    | -                    | 8   | Unit | Note |

|                                  | tency  | 501             | min | max         | min   | max    | min                  | max |      |      |

| Refresh Cycle                    |        |                 |     |             |       |        |                      |     |      |      |

| Self Refresh Exit Time           |        | $t_{\sf SREX}$  | 2   | _           | 2     | _      | 2                    | _   | CLK  | 6    |

| Total Self Refresh Exit Time     |        |                 |     | LKs +<br>RC |       | 2 CLK  | s + t <sub>R</sub> ( | С   |      | 6    |

| Refresh Period for Non-Self R    | efresh | $t_{REF}$       | _   | 32          | _     | 32     | _                    | 32  | ms   | 7    |

| Read Cycle                       |        |                 |     |             |       |        |                      |     |      |      |

| Data Out Hold Time               |        | t <sub>OH</sub> | 2.5 | _           | 2.5   | _      | 3                    | -   | ns   |      |

| Data Out to Low Impedance T      | ime    | $t_{LZ}$        | 0   | _           | 0     | _      | 0                    | _   | ns   |      |

| Data Out to High Impedance 7     | ime    | $t_{HZ}$        | 3   | 8           | 3     | 8      | 3                    | 8   | ns   | 8    |

| Write Cycle                      |        |                 |     |             |       |        |                      |     |      |      |

| Data In Setup Time               |        | $t_{DS}$        | 2   | _           | 2     | _      | 2.5                  | -   | ns   |      |

| Data In Hold Time                |        | $t_{DH}$        | 1   | _           | 1     | _      | 1                    | 1   | ns   |      |

| Write recovery time              |        | $t_{WR}$        | 6   | -           | 7     | _      | 8                    | -   | ns   |      |

| Block Write Cycle                |        |                 |     |             |       |        |                      |     |      |      |

| Block Write Cycle Time           |        | $t_{BWC}$       | 12  | _           | 14    | _      | 16                   | _   | ns   |      |

| Block Write to Precharge delay   | у      | $t_{BWR}$       | 12  | _           | 14    | _      | 16                   | _   | ns   |      |

| Miscellaneous                    |        |                 |     |             |       |        |                      |     |      |      |

| Mode Register command to command |        | $t_{RSC}$       | 2   | -           | 2     | -      | 2                    | _   | CLK  |      |

Table 14 Notes see next page

#### **Electrical Characteristic**

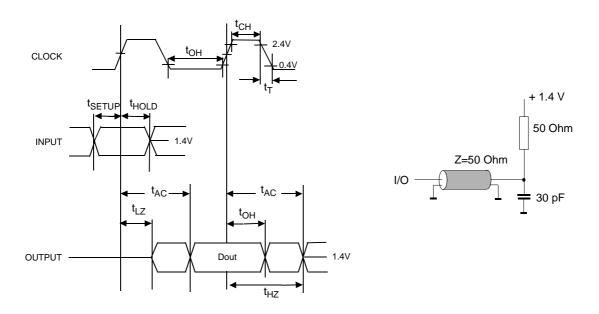

Note: 1)  $T_A = 0$  to  $70 \,^{\circ}$ C;  $V_{SS} = 0$  V;  $V_{DD} = 3.3 \, \text{V} \pm 0.3 \, \text{V}$ ,  $t_T = 1 \, \text{ns}$

2) AC timing tests have  $V_{IL} = 0.4V$  and  $V_{IH} = 2.4V$  with the timing referenced to the 1.4 V crossover point. The transition time is measured between  $V_{IH}$  and  $V_{IL}$ . All AC measurements assume  $t_T$ =1ns with the AC output load circuit shown

Note: 3) If clock rising time is longer than 1ns, a time  $(t_T/2 - 0.5)$ ns has to be added to this parameter.

- 4) If tT is longer than 1ns, a time  $(t_T 1)$ ns has to be added to this parameter.

- 5) These parameter account for the number of clock cycle and depend on the operating frequency of the clock, as follows:

Number of clock cycle = specified value of timing period (counted in fractions as a whole number)

- 6) Self Refresh Exit is a synchronous operation and begins on the second positiv edge after CKE returns high. Self Refresh Exit is not complete until a time period equal to  $t_{RC}$  is satisfied once the Self Refresh Exit command is registered.

- 7) Any time that the refresh Period has been exceeded, a minimum of two Auto (CRB) Refresh commands must be given to "wake-up" the device.

- 8) Referenced to the time which the output achieves the open circuit condition, not to output voltage levels.

## **Electrical Characteristic**

## 3.4 Clock Frequency and Latency

| Darameter                       |       | Symbol                          |     | Unit |     |     |     |      |

|---------------------------------|-------|---------------------------------|-----|------|-----|-----|-----|------|

| Parameter                       |       | Symbol                          | - 6 |      | - 7 |     | - 8 | Unit |

| Clock Frequency                 | max.  |                                 | 166 | 125  | 143 | 125 | 125 | MHz  |

| Clock Cycle Time                | min.  | t <sub>CK</sub>                 | 6   | 8    | 7   | 8   | 8   | ns   |

| CAS Latency                     | min.  | $t_{AA}$                        | 3   | 2    | 3   | 2   | 3   | CLK  |

| RAS to CAS Delay                | min.  | $t_{RCD}$                       | 3   | 3    | 3   | 3   | 3   | CLK  |

| Bank Active Cycle Time          | min.  | $t_{RAS}$                       | 8   | 6    | 7   | 6   | 7   | CLK  |

| Bank Active Cycle Time          | max.  | $t_{RAS}$                       | 100 | 100  | 100 | 100 | 100 | μs   |

| Precharge Time                  | min.  | $t_{RP}$                        | 3   | 3    | 3   | 3   | 3   | CLK  |

| Bank Cycle time                 | min.  | $t_{RC}$                        | 11  | 9    | 10  | 9   | 10  | CLK  |

| Last Data In to Precharge       | min.  | $t_{WR}$                        | 1   | 1    | 1   | 1   | 1   | CLK  |

| Last Data In to Active/ Refresh | min.  | $t_{\text{WR}} + t_{\text{RP}}$ | 4   | 4    | 4   | 4   | 4   | CLK  |

| Bank to Bank Delay Time         | min.  | $t_{RRD}$                       | 2   | 2    | 2   | 2   | 2   | CLK  |

| CAS to CAS delay time           | min.  | $t_{\sf CCD}$                   | 1   | 1    | 1   | 1   | 1   | CLK  |

| Write Latency                   | fixed | $t_{WL}$                        | 0   | 0    | 0   | 0   | 0   | CLK  |

| DQM Write Mask Latency          | fixed | $t_{\sf DQW}$                   | 0   | 0    | 0   | 0   | 0   | CLK  |

| DQM Data Disable Latency        | fixed | $t_{DQZ}$                       | 2   | 2    | 2   | 2   | 2   | CLK  |

| Clock Suspend Latency           | fixed | $t_{\mathrm{CSL}}$              | 1   | 1    | 1   | 1   | 1   | CLK  |

| Block Write Cycle Time          | fixed | t <sub>BWC</sub>                | 2   | 2    | 2   | 2   | 2   | CLK  |

Table 15

**Package Outlines**

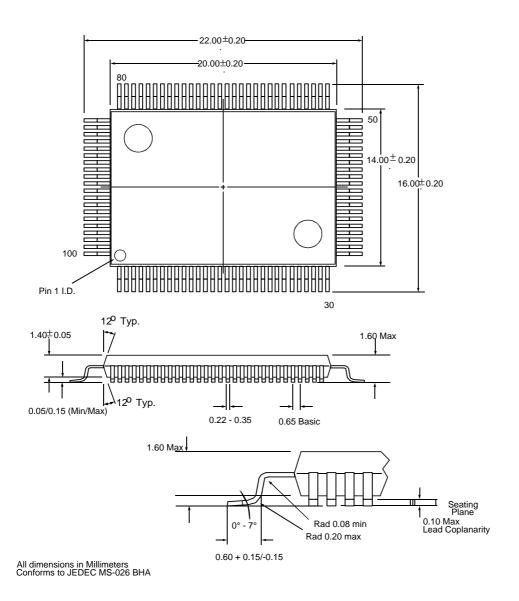

## 4 Package Outlines

Plastic Package TQFP-100 (20x14mm<sup>2</sup>, 0.65mm lead pitch) Thin small outline package, SMD

**Package Outlines**